|

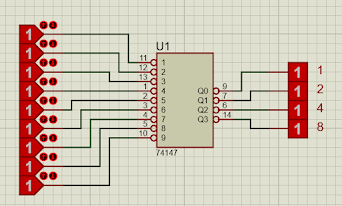

| Gambar 8.14 |

jika X0 berlogika 1 maka output Y U1 berlogika 1 kemudian masuk ke OR dimana kaki 1 berlogika 1 dan kaki 2 berlogika 0 menghasilkan output berlogika 1 sesuai dengan prinsip kerja gerbang OR. sebaliknya jika X0 berlogika 0 maka output Y U1 akan berlogika 0 (kaki 1) dan kaki 2 dalam keadaan berlogika 0 sehingga 0,0 akan mengasilkan output berlogika 0 sesuai dengan prinsip kerja gerbang OR.

-JIKA X1 berlogika 1 maka output Y U1 akan berlogika 0, untuk menghasilkan output dengan logika 1 maka kaki ABC bertindak sebagai input selektor, dimana input ABC akan dipilih mana bilangan binernya yang sesuai dengan angka pada kaki X1, disini yg diminta adalah X1 maka biner nya adalah 1 yaitu kaki A. untuk itu A berlogika 1 dan X1 berlogika 1 sehingga outputnya akan berlogika 1 kemudian masuk ke gerbang OR dimana kaki 2 berlogika 0 sehingga (1,0) akan menghasilkan output dengan logika 1

-JIKA X2 berlogika 1 maka outputnya akan berlogika 0, untuk membuat outputnya aktif(berlogika 1) maka diperlukan input selector pada ABC yang binernya sama, dima X2 binnernya 2, yg binnernya 2 adalah B, Maka kaki B inputnya berlogika 1 dan kaki X2 berlogika 1 menghasilkan output berlogika 1, kemudian masuk ke gerbang OR dimana kaki 2 dari gerbang OR berlogika 0 maka outputnya akan berlogika 1

-Untuk X3-X7 prinsipnya sama dengan X0-X2, dimana untuk membuat outputnya berlogika 1 maka diperlukan kaki ABC yang binernya sama dengan nilai kaki pada IC 74HC151 Sebagai kombinasi untuk mengaktifkan Kaki IC 74HC151 sehingga menghasilkan output dengan logika 1

-kemudian untuk U2 (Multiplexser) prinsipnya sama dengan U1, bedanya pada U2 terdapat inverter yang membuat logika pada kaki E aktif renda menjadi berlawanan dengan yg seharusnya karena inverter disini bertindak sebagai pembalik NOT sehingga output yang dihasilkan akan berkebalikan

dengan prinsip aktif rendah yaitu ketika di U1 E akan aktif jika berlogika 0 sedangkan pada u2 E akan aktif jika berlogika 1

Ketika D0 logika 0 tidak U1 U2 dan U3 OFF, karena tidak terhubung dengan salah satu gerbang logika OR. Ini menandakan bahwa addres dari D0 adalah 0 0 0.

Ketika D1 logika 1 maka OR 3 akan aktif karena D1 terhubung dengan salah satu kaki input OR 3. Karena salah satu kaki input OR 3 berlogika 1 maka output dari OR 3 akan menjadi 1. Ini menandakan bahwa addres dari D1 adalah 1 0 0.

ketika D2 logika 1 maka OR 2 akan aktif karena D2 terhubung dengan salah satu kaki input OR 2. Karena salah satu kaki input OR 2 berlogika 1 maka output dari OR 2 akan menjadi 1. Ini menandakan bahwa addres dari D2 adalah 0 1 0.

Ketika D3 logika 1 maka OR 2 dan OR 3 akan aktif karena D3 terhubung dengan salah satu kaki input OR 2 dan OR 3. Karena salah satu kaki input OR 2 dan OR 3 berlogika 1 maka output dari OR 2 dan OR 3 akan menjadi 1. Ini menandakan bahwa addres dari D3 adalah 1 1 0.

Ketika D4 logika 1 maka OR 1 akan aktif karena D4 terhubung dengan salah satu kaki input OR 1. Karena salah satu kaki input OR 1 berlogika 1 maka output dari OR 1 akan menjadi 1. Ini menandakan bahwa addres dari D4 adalah 0 0 1.

Ketika D5 logika 1 maka OR 1 dan OR 3 akan aktif karena D5 terhubung dengan salah satu kaki input OR 1 dan OR 3. Karena salah satu kaki input OR 1 dan OR 3 berlogika 1 maka output dari OR 1 dan OR 3 akan menjadi 1. Ini menandakan bahwa addres dari D5 adalah 1 0 1.

Ketika D6 logika 1 maka OR 1 dan OR 2 akan aktif karena D6 terhubung dengan salah satu kaki input OR 1 dan OR 2. Karena salah satu kaki input OR 1 dan OR 2 berlogika 1 maka output dari OR 1 dan OR 2 akan menjadi 1. Ini menandakan bahwa addres dari D5 adalah 0 1 1.

Ketika D7 logika 1 maka OR 1, OR 2 dan OR 3 akan aktif karena D7 terhubung dengan salah satu kaki input OR 1, OR 2 dan OR 3. Karena salah satu kaki input OR 1, OR 2 dan OR 3 berlogika 1 maka output dari OR 1, OR 2 dan OR 3 akan menjadi 1. Ini menandakan bahwa addres dari D5 adalah 1 1 1.

Karena input dan output dari jenis encoder yang dipakai adalah aktif rendah maka

situasi adanya input dan output ditandakan dengan logika 0.

Bilangan biner dari

Q0 = 1

Q1 = 2

Q2 = 4

Q3 = 8

output dari encoder adalah penjumlahan angka biner sesuai dengan angka input

jika input 1 diaktifkan (logika 0) maka output dari Q0 akan berlogika 0, 1+0+0+0=1

jika input 2 diaktifkan (logika 0) maka output dari Q1 akan berlogika 0, 0+2+0+0=2

jika input 3 diaktifkan (logika 0) maka output dari Q0 dan Q1 akan berlogika 0, 1+2+0+0=3

jika input 4 diaktifkan (logika 0) maka output dari Q2 akan berlogika 0, 0+0+4+0=4

jika input 5 diaktifkan (logika 0) maka output dari Q0 dan Q2 akan berlogika 0, 1+0+4+0=5

jika input 6 diaktifkan (logika 0) maka output dari Q1 dan Q2 akan berlogika 0, 0+2+4+0=6

jika input 7 diaktifkan (logika 0) maka output dari Q0, Q1 dan Q2 akan berlogika 0, 1+2+4+0=7

jika input 8 diaktifkan (logika 0) maka output dari Q3 akan berlogika 0, 0+0+0+8=8

jika input 9 diaktifkan (logika 0) maka output dari Q0 dan Q3 akan berlogika 0, 1+0+0+8=9

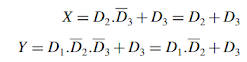

Jika D1 diaktifkan (logika 1) maka pada salah satu kaki input AND berlogika 1. Salah satu kaki AND yang lain sudah berlogika 1 yang disebabkan D2 berlogika 0 terus di inverter sehingga berlogika 1. Karena kedua kaki input AND berlogika 1 maka output dari AND adalah logika 1, sehingga pada salah satu kaki input OR 2 berlogika 1, maka output dari OR 2 adalah logika 1 pada Y.

Jika D2 diaktifkan (logika 1) maka salah satu kaki input OR 1 berlogika 1, sehingga output dari OR 1 adalah logika 1 pada X.

Jika D1 dan D2 diaktifkan (logika 1) maka salah satu kaki input OR 1 berlogika 1, sehingga output dari OR 1 adalah logika 1 pada X. Karena D2 logika 1 terus di inverter menjadi berlogika 0 pada gerbang AND, maka gerbang AND tidak aktif atau berlogika 0. Karena pada kaki input OR 2 semuanya logika 0 maka output dari gerbang OR 2 adalah berlogika 0 pada Y.

Jika D3 diaktifkan (logika 1) maka salah satu kaki input dari OR 1 dan OR 2 akan berlogika 1

sehingga gerbang OR 1 dan OR 2 outputnya menjadi logika 1 pada X dan Y

Tidak ada komentar:

Posting Komentar